.png)

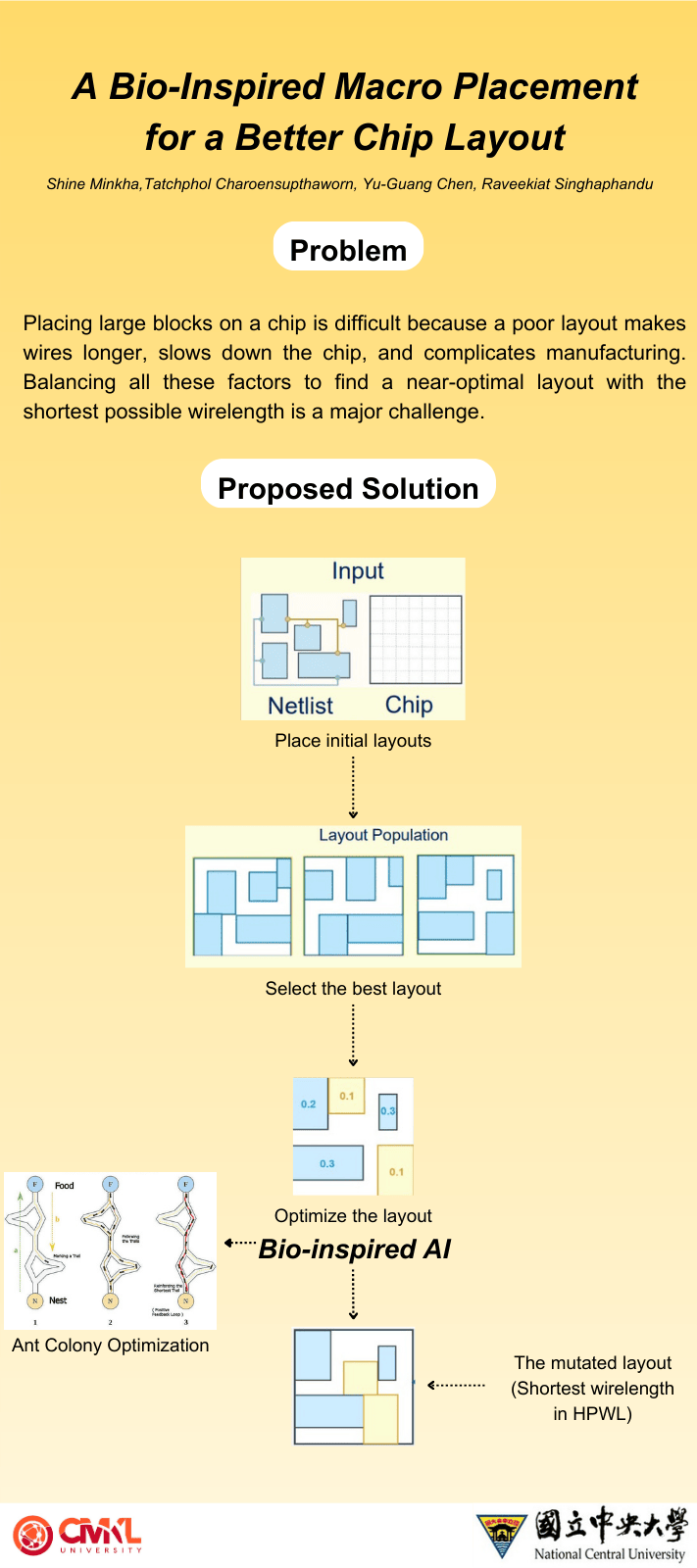

A Macro Placement Optimization Framework for Half-Perimeter Wirelength in Very-large-scale integration Design

-

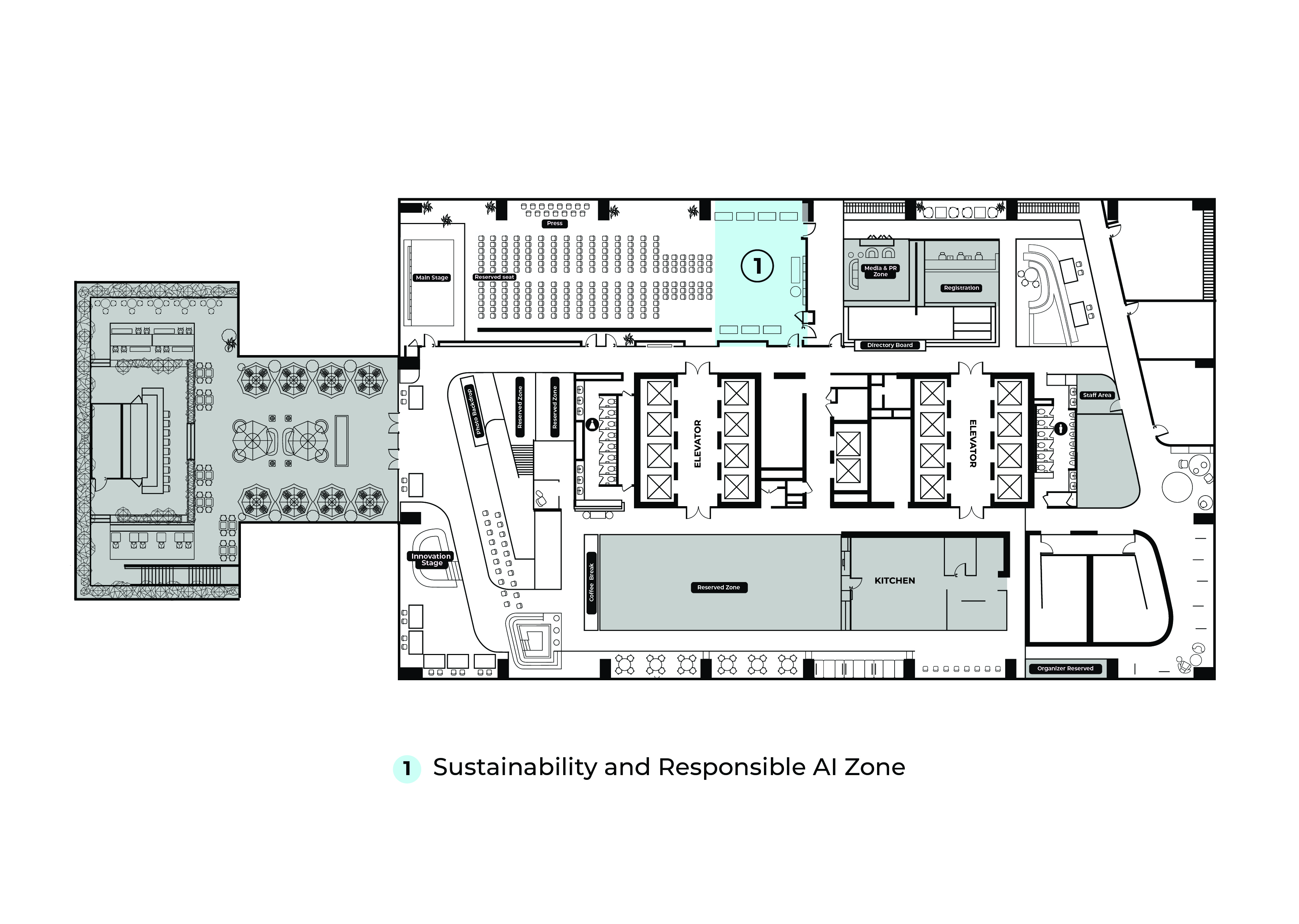

Sustainability & Responsible AI Zone

Session

Booth

speaker

No items found.

Description

This project focuses on optimizing macro placement in VLSI physical design to improve overall chip performance. The primary goal is to reduce Half-Perimeter Wirelength (HPWL), while also considering secondary metrics such as routing congestion, timing, and area utilization. By developing and evaluating placement strategies, the project aims to enhance wirelength efficiency and placement quality for large-scale integrated circuits.

location

Secure Your Seat at the Frontier

AI Innovation event.

Reserve your seat now.

DEC 12, 2025

BANGKOK , THAILAND

BANGKOK , THAILAND

REGISTER Now

.png)